spyglass学习

1 Spyglass介绍

SpyGlass是目前业界唯一可靠的RTL Sign off解决方案,可以帮助客户在设计早期发现潜在问题,保证产品质量,极大的减少设计风险, 降低设计成本。SpyGlass已经成为集成电路开发过程中必不可少的RTL-QA工具。SpyGlass作为第三代RTL代码质量分析工具的领导者, 已经被全世界的IC设计公司和IP公司广泛采用。

1.1 Spyglass技术领先优势

- 业界唯一公认的RTL sign off解决方案

- 软IP出厂质量检验必备工具

- TSMC IP 9000 采用SpyGlass

- 业界检查规则最全的检查工具,内含5000余条设计的规则

- 业界最全面的多时钟域CDC检查机制

- 业界最快速的早期DFT检查方法学

- 业界最先进的早期低功耗解决方案

- 业界唯一的SDC检查工具

- 可与设计流程上其它环节EDA工具无缝连接

- 支持深亚微米设计规则

1.2 SpyGlass子模块介绍

- SpyGlass-Lint

- 支持多种规则检查,能发现诸如Latch等代码质量问题。

- SpyGlass-CDC

- 支持所有常见的同步器;自动识别设计中复杂的握手信号和FIFO同步机制并对其进行形式验证;自动识别gray-code逻辑和re-convergent信号并对其进行形式验证。用户不需要提供任何的仿真激励和assertions来测试CDC问题,工具自动生成并进行CDC分析。

- SpyGlass-Power

- 帮助用户管理复杂的多电源和电压域:它可以验证、显示和分析多个域之间的串扰问题,并且自动修复功能可以自动的插入level-shifter和isolation逻辑。SpyGlass-Power是包括针对时钟、数据通路控制、总线和内存单元的一套完全的技术。SpyGlass-Power的最新功能还包括基于RTL代码的功耗估计和最优门控时钟设计建议。

- SpyGlass-DFT

- 包括丰富的、超过100条DFT设计规则。这些包括时钟规则、锁存器规则、布局规则、三态规则、RAM规则、扫描链规则等。SpyGlass-Test包括At-speed覆盖率预测,因此它能明确的指出今后测试的瓶颈。它不仅能报告覆盖率,还能描述出覆盖率低的原因。它统一的自动修复能力自动的更正很多扫描出的问题。

- SpyGlass-Constraints

- 自动生成对应RTL或网表的SDC以及时序异常约束;自动对时序异常进行形式验证;精确的查明SDC的语法、一致性和完整性问题,包括模块内部的、模块之间的,以及模块和整个芯片之间。SpyGlass-Constraints可以把模块级的SDC合并成芯片级的SDC;检测出SDC的不同版本和针对不同工具、不同设计阶段的SDC存在的问题。

以上构成分析RTL问题的完整平台,全面的解决RTL设计中所存在的各方面问题。

1.3 Spyglass基本概念

对于Spyglass,我们先要知晓一些基本概念:

- Rule: 是SpyGlass 进行RTL分析的最小单位。

- Goal: 是一系列相关Rule的集合,组合起来完成RTL分析的某个特定任务. user可以用GuideWare定义好的Goal, 也可根据工程项目要求来选择一系列rule的集合形成自定义 GUI里面点Goal的button来选择设定, 也可在Prj file 里定义。

- Sub-Methodology: 是一系列相关Goal的集合, 用以达成某方面特定目标, 如完成CDC check。

- SGDC: Constraints 文件, 主要包含clock和reset等约束信息。

- Waiver: 用以过滤一些结果的文件。

- Severity: report结果中分Fatal, Error, Warning和INFO四等级信息。

- Parameter: 可以在进行RTL分析之前设定某些参数, 对检查过程进行一些约束。

1.4 Spyglass流程阶段

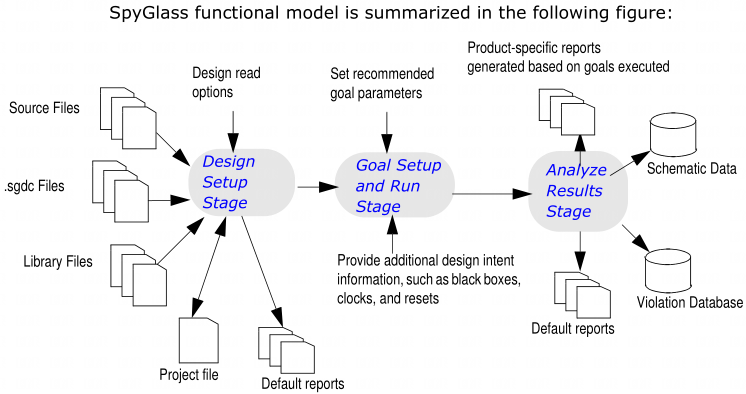

Spyglass的原理流程分为三个阶段:设置阶段、目标和运行阶段、分析结果阶段,如下所示:

2 Spyglass界面操作

2.1 读取设计文件

(1)Linux的terminal输入spyglass &,这便打开了Spyglass工具的图形界面。

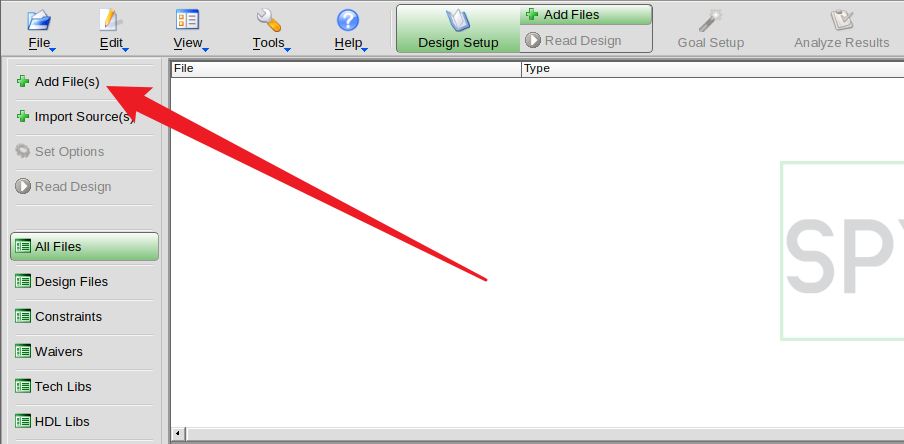

(2)点击工具左侧的“Add Files”,加载设计文件。

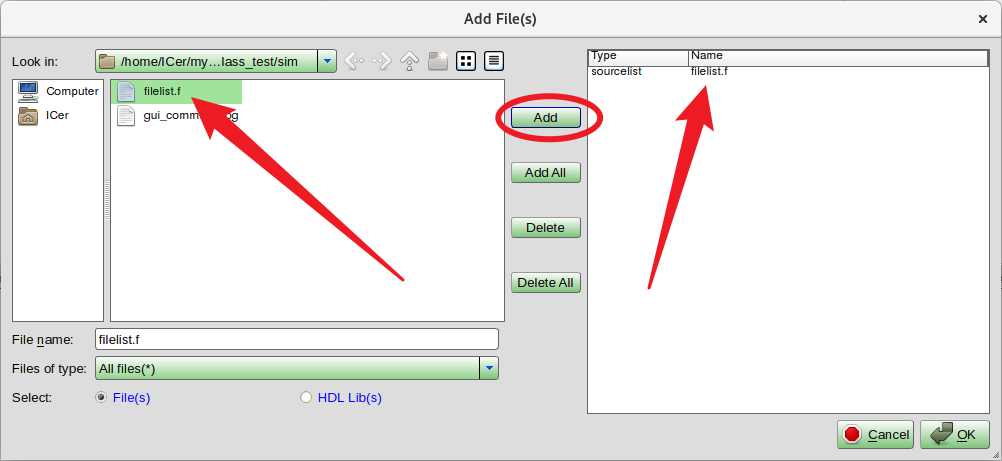

(3)弹出的选中界面选中所需的Verilog文件,如果准备好了filelist,可以直接选中filelist,然后点击Add按钮

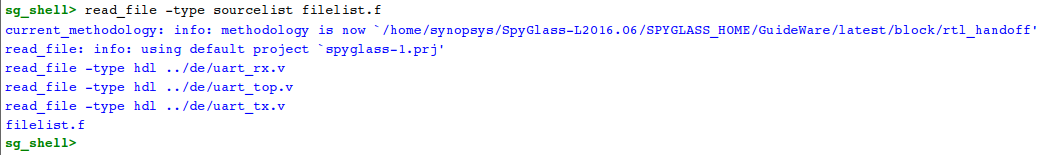

此时Spyglass界面下方的sg_shell界面会打印出读取到文件的相关信息:

2.2 设置顶层模块

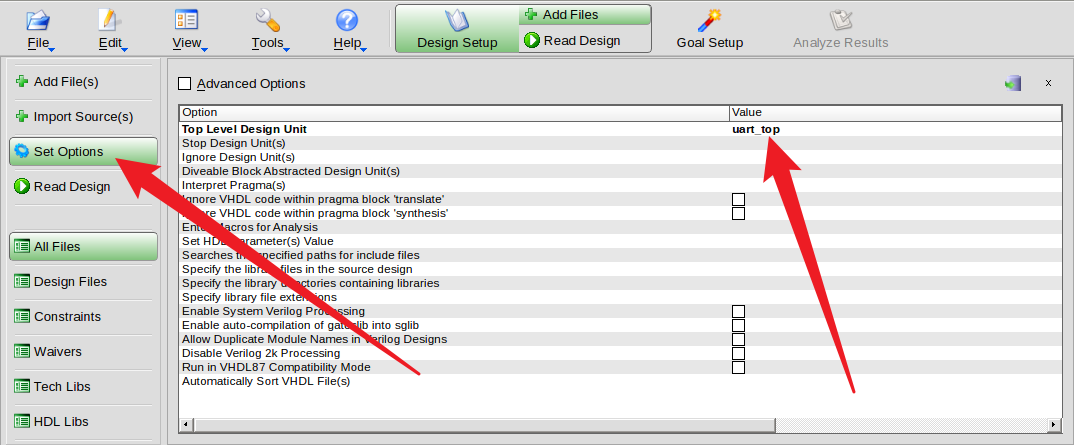

(1)点击“Set Options”,然后双击“Top Level Design Unit”的Value框,输入顶层模块名“uart_top”,再敲回车。

2.3 编译设计

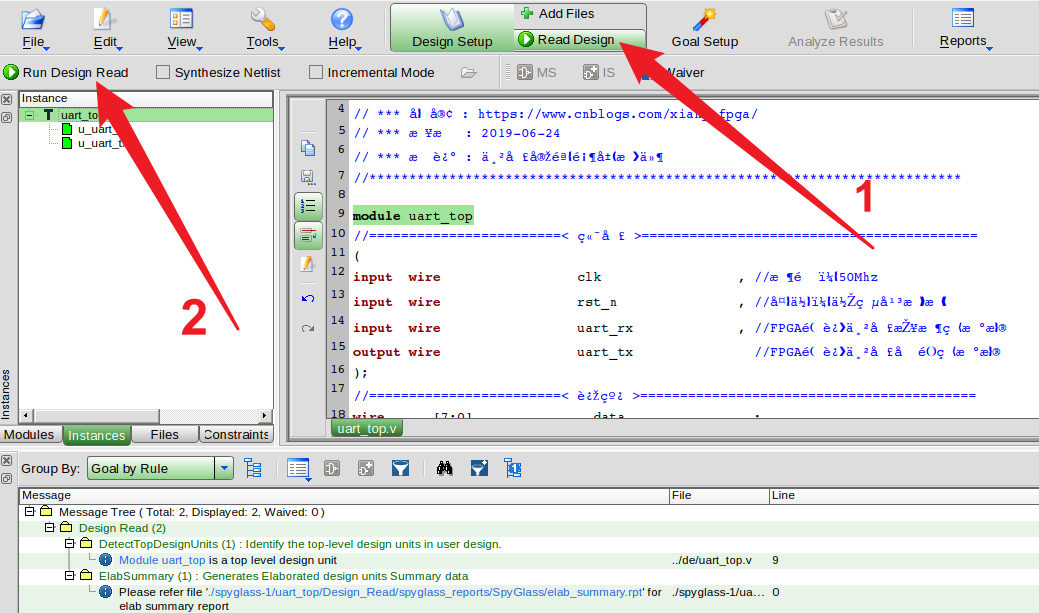

先点击上方的“Read Design”,再点击左侧的“Run Design Read”,开始进行文件编译和分析,结果见下方窗口。

这次的文件编译没有问题,界面中的Instances出现了目录结构,都是绿色的。

如果文件不存在,则会报错提醒,同时Instances里的对应文件会变成黑色。Instance下文件的颜色含义如下:

- 绿色表示已准备好进行分析但尚未在内部综合;

- 黑色表示无法分析该块(黑框);

- 白色表示该模块是可综合的;

2.4 静态分析lint

Lint分析不要求完整的工程文件,因此非常方便分工合作,每个人只负责自己这部分的检查即可。

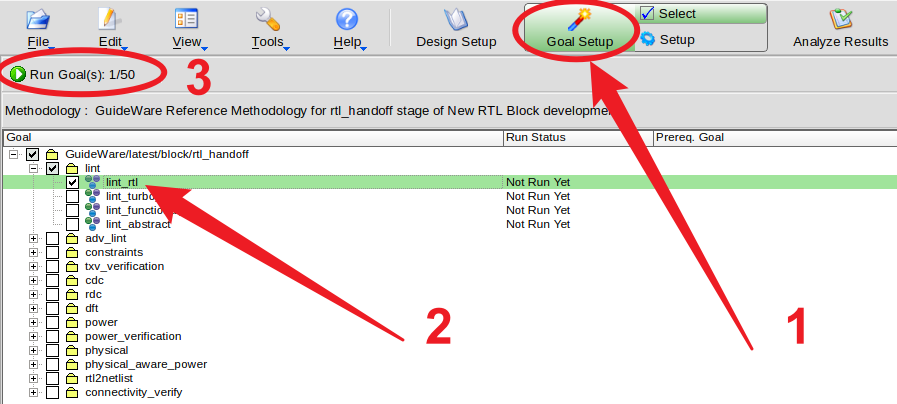

(1)先点击上面的“Goal Setup”,然后选中lint下的lint_rtl,最后点击“Run Goal”。

注意:如果有特殊需求,可以在lint_rtl里右键选择Edit Rules and Parameters来修改或waive规则。

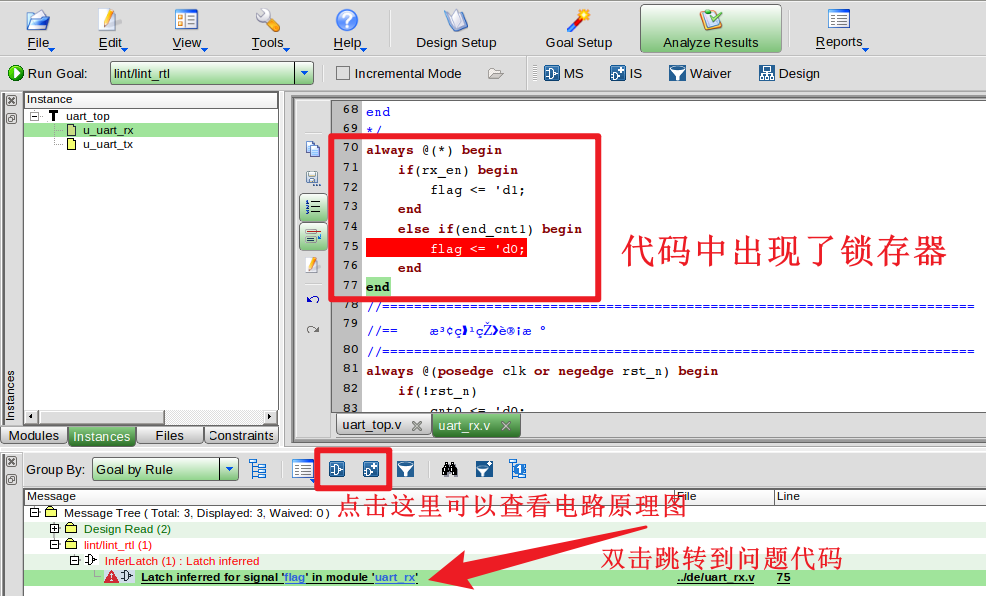

(2)下方窗口显示出了分析结果,这里是出现了一个Latch,双击该警告会跳转到出问题的代码。思考后发现这里用了组合逻辑,但if后没有跟else,因此出现了锁存器。

(3)红色信息表示错误,橙色信息表示警告,绿色信息表示正常。

(4)选中违规信息,右键选择Waive Selected Messages可以忽略掉某种类型的检查。

(5)点击方框中的类似图像界面的符号,还可以查看设计的电路原理图

2.5 状态机完整性分析

Spyglass还可以用于检查状态机的完整性,这里重新建立工程,引入一个写有状态机的Verilog。

(1)编辑sgdc文件

做状态机的结构完备性检查时,需要用到Spyglass 的工程约束文件,叫做SGDC,这是一种类似SDC的约束文件,全称是:Spyglass Design Constraints。

新建一个spyglass.sgdc文件,内容如下所示:

1 | #当前设计工程,需要填写 top 模块名称:FSM_3 |

(2)状态机分析

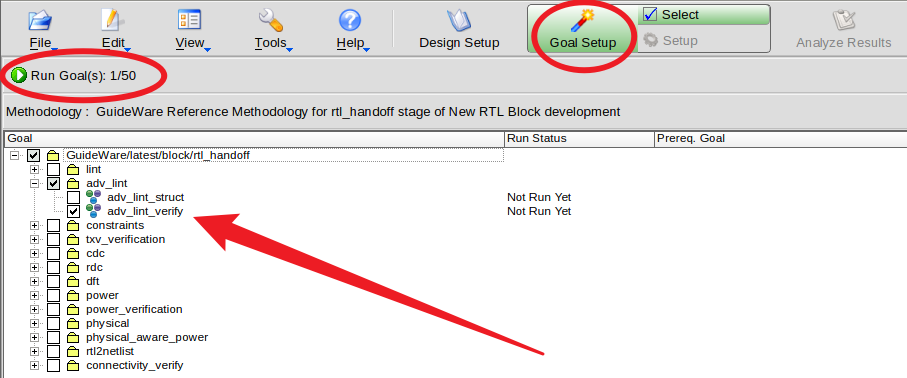

读取设计文件FSM_3.v和上面写好的约束文件spyglass.sgdc,设置顶层模块为FSM_3,然后点击“Goal Setup”,勾选“adv_lint_verify”,然后点击“Run Goal”,等待报告结果。

(3)查看状态机

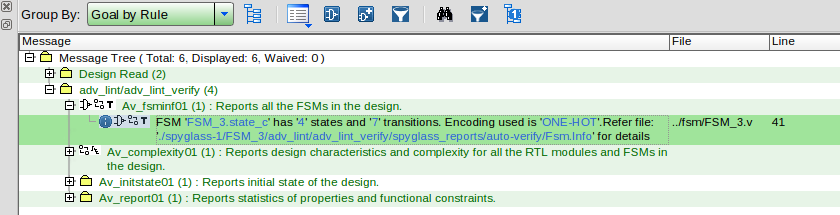

如果设计没有问题,那么下方窗口显示如下,发现了存在状态机。

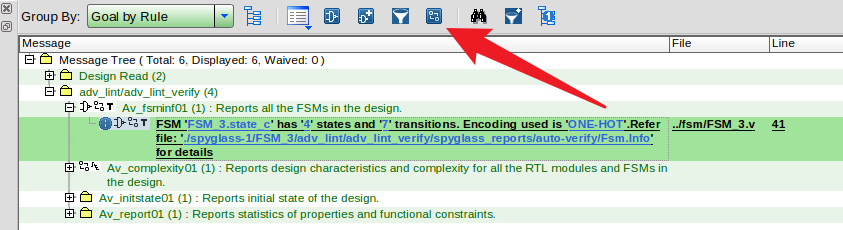

双击该行后,弹出一个“Text Container”报告,点击OK关闭它,这时界面出现了一个新的图标,点击它。

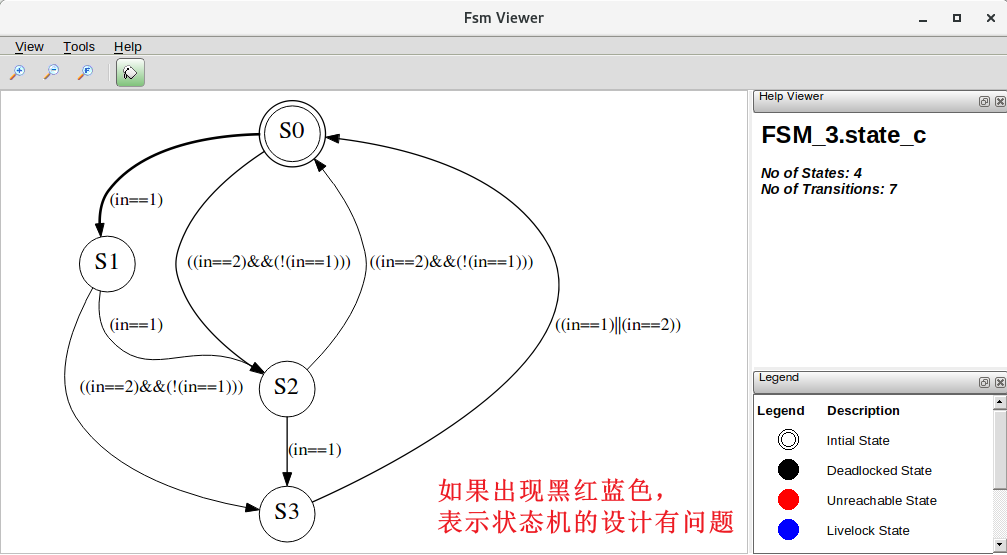

弹出了状态机图,可以放大和缩小,查看状态机跳转情况。

- 红色:无法到达的状态;

- 黑色:锁死状态,无法跳出;

- 红色线:带有箭头是已经分析的死跳转;

- 红色虚线:带有箭头是死跳转驱动;

- 蓝色:活锁状态,就是在几个状态中反复循环无法回到初始态;

3 Spyglass命令操作

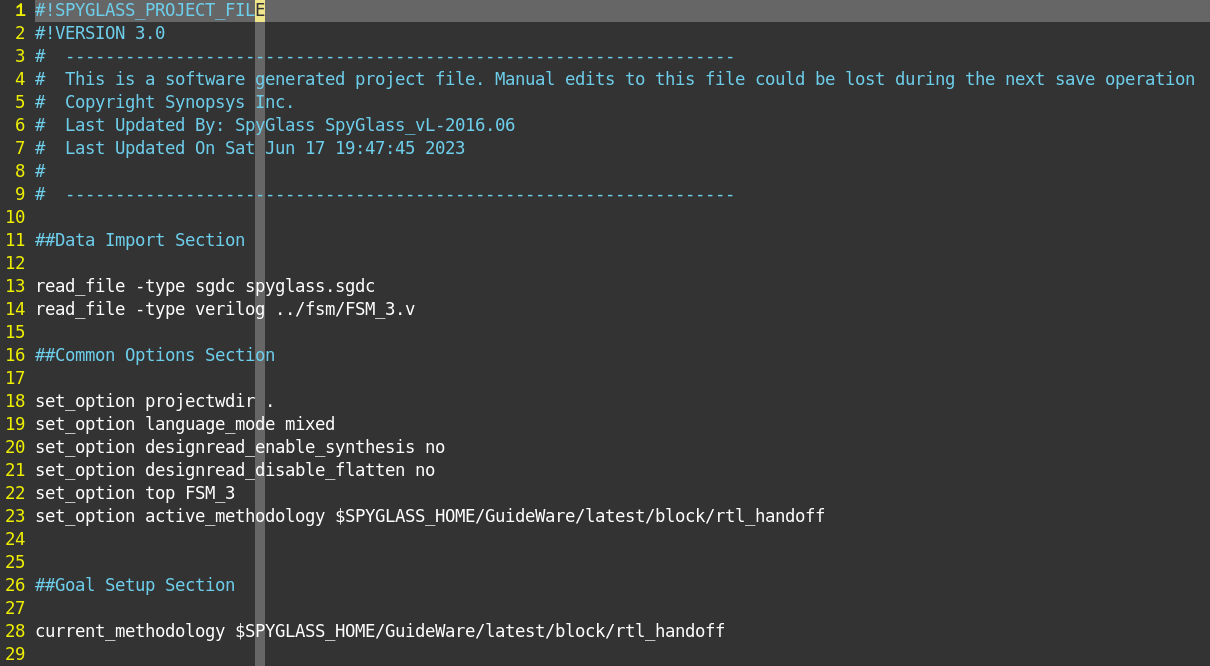

上述操作完成后,退出Spyglass,提示是否保存工程,将其保存为FSM_3.prj,用文本编辑器打开,内容如下:

这正是我们刚刚操作过的spyglass步骤,那么如何直接采用这些命令呢?

3.1 读取和编译

在当前存在FSM_3.prj文件的目录下,使用-batch选项即可自动完成Spyglass的读取和编译,命令如下:

1 | spyglass -project FSM_3.prj -designread -batch |tee spyglass.log |

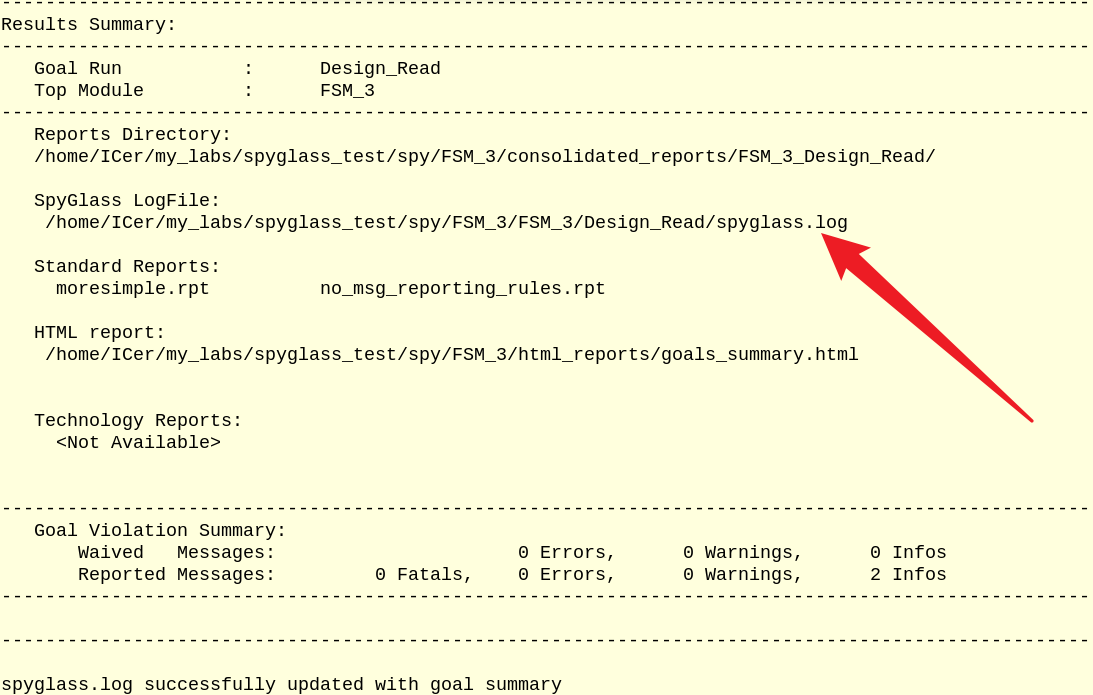

|tee spyglass.log是我另外加的,目的是为了让读取和编译的报告打印到当前目录下的spyglass.log文件中,其实不用加这句也行,因为Spyglass会自动将结果打印到当前目录下FSM_3/FSM_3/Design_Read/spyglass.log中。

3.2 获取Goal列表

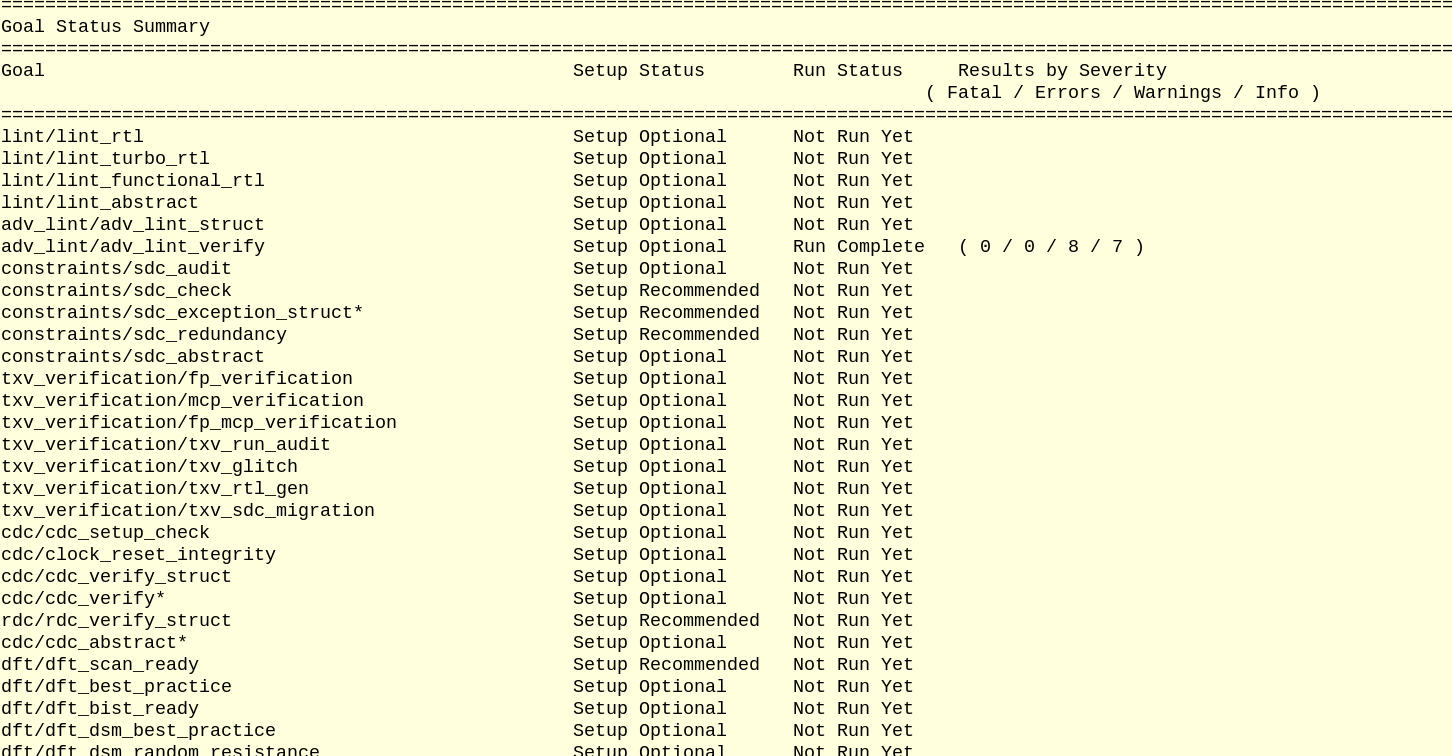

通过下面命令可以获取可用的Goal列表:

1 | spyglass -project FSM_3.prj -showgoals |

3.3 运行Goal分析

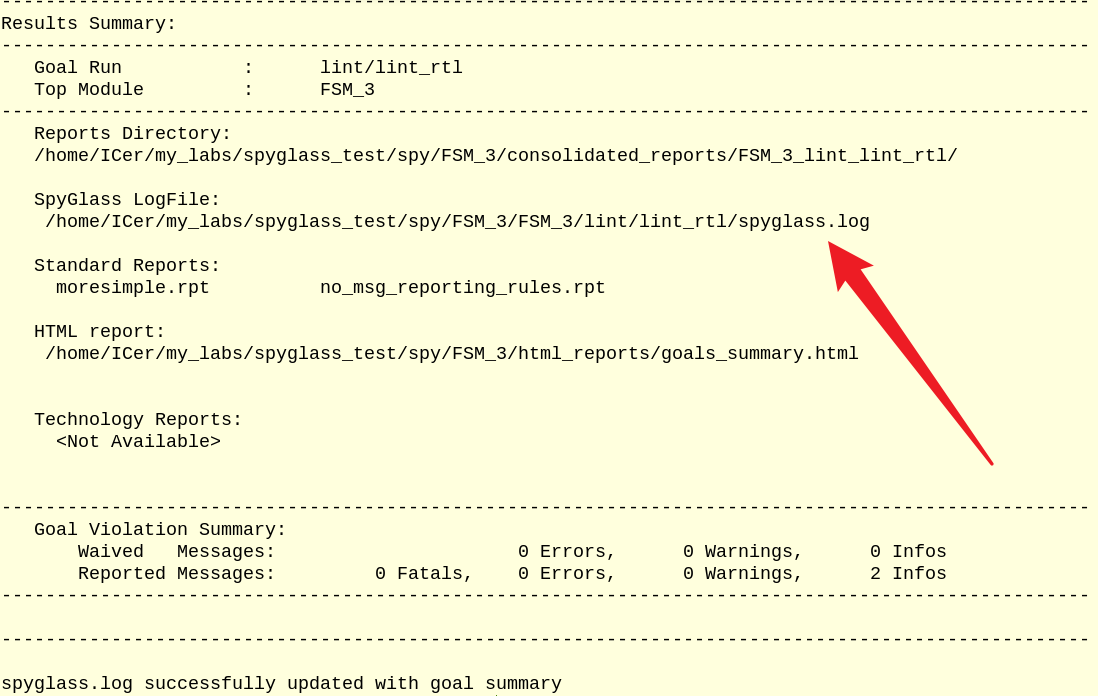

我们试着跑“lint/lint_rtl”分析,输入如下指令:

1 | spyglass -project FSM_3.prj -goals lint/lint_rtl -batch |

terminal在不断显示运行结果了,运行完毕后,打印信息提示我们可以到下列文件查看完整log文件:

参考资料:

[Spyglass的CDC检查 - Galois_V - 博客园 (cnblogs.com)](https://www.cnblogs.com/WenGalois123/p/17459291.html#:~:text=Spyglass的CDC检查 接着前面Lint检查之后需要对RTL进行CDC检查,以下是简单的步骤。 1.在完成lint检查后,也就是确保没有语法错误之后,点击Goal Setup,然后勾选主窗口下cdc_setup_check,然后点击Run Goal,(s) ,当运行完成,会自动弹出Analyze Result窗口。 2.得到分析结果后, cdc%2Fcdc_setup_check文件夹消息。)